INCLUDING:

### Chris A. Ciufo

Thinking outside the box

### Field Intelligence

1553's well-deserved longevity

### Mil Tech Insider

I/O mezzanines in FPGA computing

### **Legacy Software Migration**

**ALT Software:**

Managing legacy graphics software

# Annapolis Micro Systems

The FPGA Systems Performance Leader

# High Performance Signal and Data Processing in Scalable FPGA Computing Fabric

GEOINT, Ground Stations, SDR, Radar, Sigint, COMINT, ELINT, DSP, Network Analysis, Encryption, Image Processing, Pattern Matching, Oil & Gas Exploration, Financial Algorithms, Genomic Algorithms

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE

Between FPGAs and Standard Output Modules

Between FPGAs and Storage Arrays

Ultimate Modularity

From 1 to 8 Virtex 4, 5 or 6 FPGA/Memory Modules

Input/Output Modules Include:

Quad 130 MSPS thru Quad 550 MSPS A/D

1.5 GSps thru 5.0 GSps A/D, Quad 600 MSps D/A,

Dual 1.5 GSps thru 4.0 GSps D/A

Infiniband, 10G, 40G or 100G Ethernet or SFPDP

VME/VXS/VPX, IBM Blade, PCI-X/PCI Express, PMC/XMC, MicroTCA

No Other FPGA Board Vendor Streams This Volume of Data Real Time Straight Into the Heart of the Processing Elements and Then Straight Back Out Again

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com USA (410) 841-2514 www.annapmicro.com

### SSD Industrial Solid State Disk - Capacity to 512GB

2.5" SATA 20000 Read:230MB/s(max.) Write:160MB/s(max.)

1.8" SATA 10000 Read:160MB/s(max.) Write:140MB/s(max.)

2.5" ATA 8000-J Read: 85MB/s(max.) Write: 75MB/s(max.)

### i-DIMM Series

Embedded Solution: Low Profile, Wide Temp. Server/Workstation Solution: w/ECC, w/ECC w/PLL, w/ECC w/R Printer Solution

MiniPCle Series

### 8000 Series-EDC/iCF

Vertical type 40pin

iCF Write Protect Series Read: 80MB/s(max.) Write: 75MB/s(max.)

CFast 100

2GB~16GB Data Transfer Rate Read-100MB/sec. (max.) Write-50MB/sec. (max.)

Low Profile / Vertical Type Read: 24MB/s(max.) Write: 14MB/s(max.)

# EMBEDDED SYSTE

July/August 2010 Volume 6 Number 5

### **COLUMNS**

### Field Intelligence

MIL-STD-1553's longevity is well deserved

By Duncan Young

### Mil Tech Insider

I/O mezzanines for FPGA-based reconfigurable computing

By Steve Edwards

### **Legacy Software Migration**

Managing legacy graphics and user interface software

By Mark Snyder, ALT Software

### **Crosshairs Editorial**

42 Thinking outside the box:

> Why did Curtiss-Wright and Kontron both just buy systems integration houses?

By Chris A. Ciufo

### **DEPARTMENTS**

14-15 **Daily Briefing: News Snippets**

By Sharon Hess

40-41 **Editor's Choice Products**

### ON THE COVER:

In July 1945, the Army's successful Trinity test was the culmination of America's Manhattan Project, and proved that a nuclear weapon was not only feasible, but frighteningly lethal. During the war, the two brute force nuclear bombs required specially modified B-29s to deliver ordnance on target. Today, precision strike weapons carried by smaller UAS platforms can eliminate hard and soft targets with minimal collateral damage. The secret to these weapons is low-cost, lightweight COTS hardware and sophisticated software. See stories on pages 22, 26, 32, and 36 (Image courtesy of http://listsoplenty.com)

ISSN: Print 1557-3222

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2010 OpenSystems Media © 2010 Military Embedded Systems

### Hardware: Security via RFID

RFID and asset authentication: **Enabling true security measures**

By Neil Mitchell, MIKOH Corporation Limited

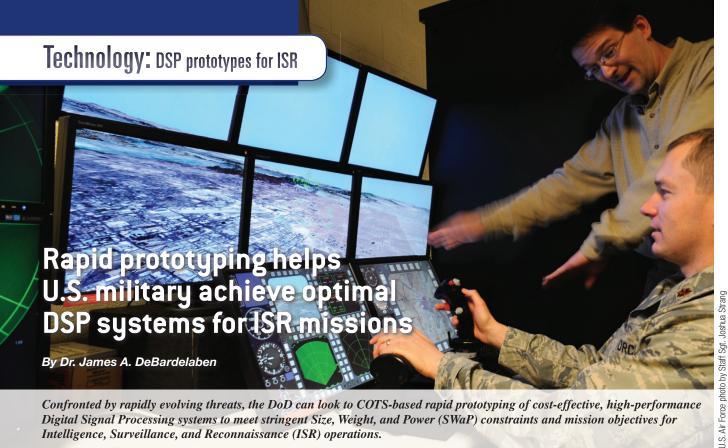

### Technology: DSP prototypes for ISR

18 Rapid prototyping helps U.S. military achieve optimal DSP systems for ISR missions

By Dr. James A. DeBardelaben, IvySys Technologies, LLC

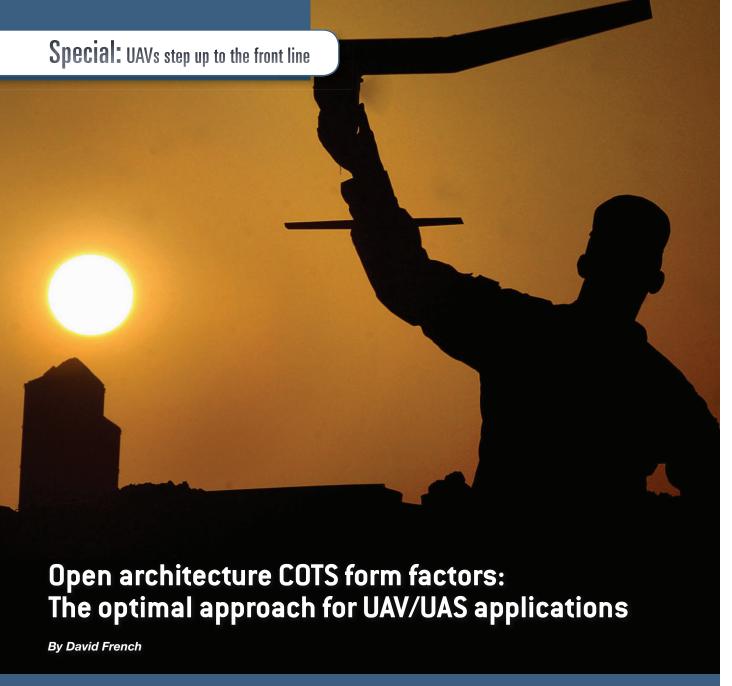

### Special: UAVs step up to the front line

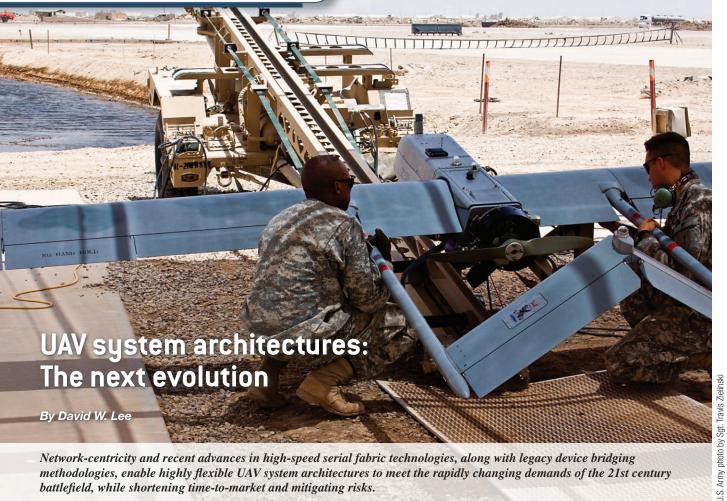

**UAV** system architectures: The next evolution By David W. Lee, Curtiss-Wright Controls Electronic Systems

26 Open architecture COTS form factors: The optimal approach for UAV/UAS applications

By David French, Kontron

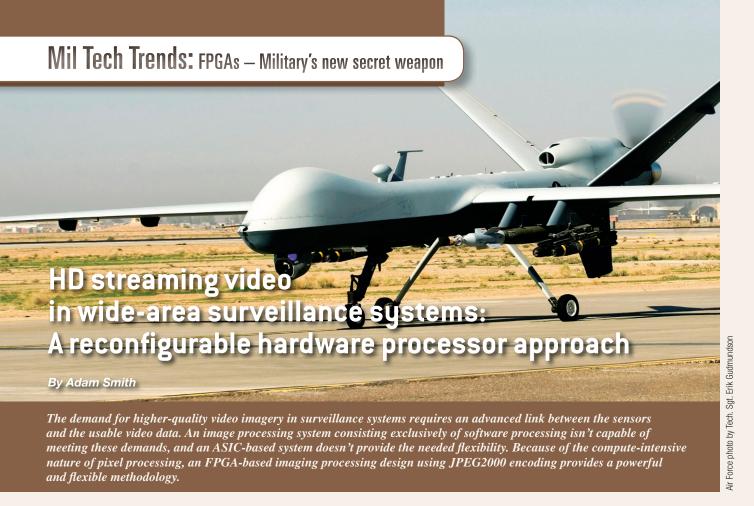

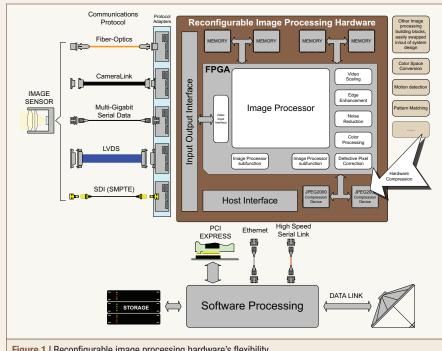

### Mil Tech Trends: FPGAs - Military's new secret weapon

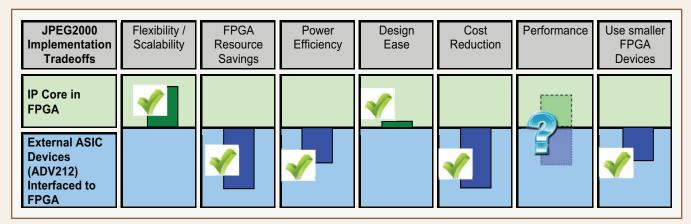

HD streaming video in wide-area surveillance systems:

A reconfigurable hardware processor approach

By Adam Smith, Alpha Data Inc.

Accelerating floating-point designs on FPGAs using math.h functions

> By Michael Kreeger, Kreeger Research and Brian Durwood, Impulse Accelerated Technologies

### E-CASTS

http://ecast.opensystemsmedia.com

Seven strategies to optimize quality with frictionless delivery

August 31st • 11am MST Presented by: IBM, Wind River

### **DO-178B Level A Programming Environment**

September 9th • 10am MST Presented by: Esterel, Wind River

### WEB RESOURCES

Subscribe to the magazine or E-letter Live industry news • Submit new products

http://submit.opensystemsmedia.com

### White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

# Mission Critical Control the sea Cutting-edge reliability Royal Navy Astute Class nuclear-powered attack submarine. Thales' periscope provides

### Wind River embedded solutions deliver the breakthrough dependability and performance essential to innovation.

To control the sea, a submarine depends on remaining invisible. But when designing and building a sub, visibility is critical. That's why Thales partnered with Wind River to create a breakthrough in periscope design for the Royal Navy's new Astute-Class submarine.

Relying upon the proven innovation, reliability and performance of our VxWorks RTOS platform, Thales developed a state-of-the-art optronic imaging system that provides stable, high-resolution views in the world's most demanding conditions.

It's the kind of teamwork and support that's made Wind River a trusted leading provider of advanced embedded solutions for aerospace and defense.

To see how Wind River can help you innovate with confidence, download our Mission Critical Toolkit at www.windriver.com/missioncritical/security.

WIND RIVER

a 360° scan of the surface above with minimal risk

of detection.

® 2010 Wind River Systems, Inc. The Wind River logo is a trademark, and Wind River is a registered trademark of Wind River Systems, Inc. Other marks are the property of their respective owners. Photograph by: Jonathan Massey; © Crown Copyright/MOD, image from www.photos.mod.uk

### **ADVERTISER INFORMATION**

#### Advertiser/Ad title Page

- 2 Annapolis Micro Systems, Inc. -High performance signal and data processing

- 35 BittWare, Inc. - Essential building blocks

- 17 CMP Techinsights – A new era, a new ESC

- **Curtiss-Wright Controls Embedded** Computing - Reduce your development time and costs

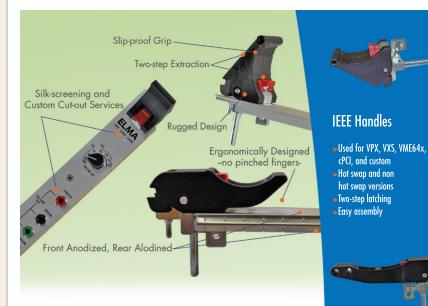

- 37 Elma Electronic - The industry's choice in VPX handles and panels

- Engineering Design Team Inc. -21 PCIe x8 LX + PCIe 1553b

- 13 Excalibur Systems, Inc. - Dragon

- 43 GE Intelligent Platforms, Inc. - It's an open specification

- 3 InnoDisk - Experience fast and furious

- 30 Interface Concept - Trust a worldwide expert

- 19 Microhard Systems Inc. - Wireless innovation

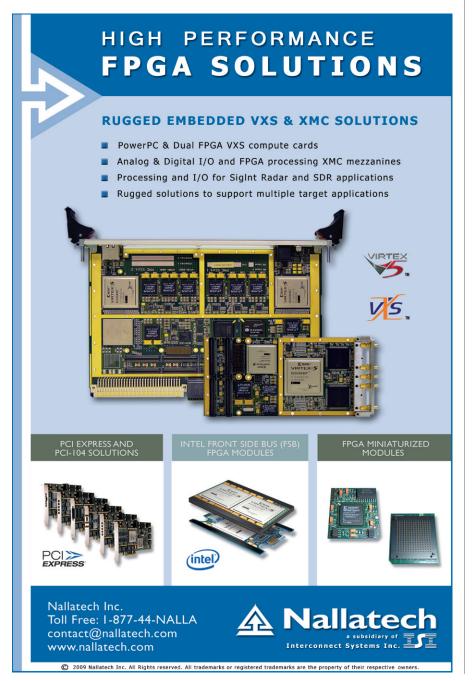

- 24 Nallatech - High performance FPGA solutions

- North Atlantic Industries Multifunction 28

- 31 Parvus Corporation – Qualified to perform

- Phoenix International RPC12 ruggedized 12 3U Fibre Channel RAID system

- 39 Sanmina-SCI - Embedded SSD solutions

- Schroff a brand of Pentair Electronic 27 Packaging - Schroff understands the demands

- 25 Sealevel Systems, Inc. - The right connection creates incredible power

- 21 TEWS Technologies LLC - COTS I/O solutions

- Trident Space & Defense Proteus 31 Series SSDs

- 29 Tri-M Systems Inc. - PC/104 Can-Tainer

- 34 Tri-M Systems Inc. - 100Mhz PC/104 module

- Vector Electronics & Technology, Inc. -7 VME/cPCI ruggedized chassis

- 10 White Electronic Designs/Microsemi -We create space

- 5 Wind River Aerospace & Defense Division -Mission critical

- 23 Z Microsystems, Inc. - Rugged rack mounted servers

### **E-LETTER**

www.mil-embedded.com/eletter

- Securing wireless Local Area Network interconnections with Layer 2 encryption By Juan Asenjo, Thales e-Security

- Raising the bar for security needs: What does "secure boot" really mean? By J. Ryan Kenny, CPU Tech

- Requirements tracing tools can manage legacy systems, too By Pete Decher, Mentor Graphics

# Military EMBEDDED SYSTEMS

DSP-FPGA.com

PC/104 TO FACTORS TO SMALL FOR THE POST OF THE POST OF

Embedded COMPUTING

### Military & Aerospace Group

Chris Ciufo, Group Editorial Director cciufo@opensystemsmedia.com

Sharon Hess, Assistant Managing Editor sharon\_hess@opensystemsmedia.com

Jennifer Hesse, Assistant Managing Editor jhesse@opensystemsmedia.com

Terri Thorson, Senior Editor (columns) tthorson@opensystemsmedia.com

Monique DeVoe, Web Content Editor mdevoe@opensystemsmedia.com

Hermann Strass, European Representative hstrass@opensystemsmedia.com

Konrad Witte, Senior Web Developer

Steph Sweet, Creative Director

Joann Toth, Senior Designer

David Diomede, Art Director

Phyllis Thompson Circulation/Office Manager subscriptions@opensystemsmedia.com

### Sales Group

Dennis Doyle, Senior Account Manager ddoyle@opensystemsmedia.com

Tom Varcie, Senior Account Manager tvarcie@opensystemsmedia.com

Rebecca Barker, Strategic Account Manager rbarker@opensystemsmedia.com

### **Bridget Hildebrand**

Strategic Account Manager bhildebrand@opensystemsmedia.com

Christine Long, Digital Content Manager clong@opensystemsmedia.com

### **International Sales**

Dan Aronovic, Account Manager - Israel daronovic@opensystemsmedia.com

Sally Hsiao, Account Manager - Asia sally@aceforum.com.tw

### Regional Sales Managers

Barbara Quinlan, Midwest/Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Sydele Starr, Northern California sstarr@opensystemsmedia.com

Ron Taylor, East Coast/Mid Atlantic rtaylor@opensystemsmedia.com

### **Ad Coordinator**

### Steph Sweet

ssweet@opensystemsmedia.com

### **Reprints and PDFs**

Nan Holliday 800-259-0470

republish@opensystemsmedia.com

### Editorial/Business Office

16626 E. Avenue of the Fountains, Ste. 203 Fountain Hills, AZ 85268 Tel: 480-967-5581 Fax: 480-837-6466

Website: www.opensystemsmedia.com Publishers: John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial: Rosemary Kristoff

Vice President Marketing & Sales: Patrick Hopper

phopper@opensystemsmedia.com Business Manager: Karen Layman

# VECTOR

ELECTRONICS & TECHNOLOGY, INC. A FINE TECHNOLOGY GROUP

## VME / cPCI® Ruggedized Chassis

- Well suited for Military / Aeronautics

- **⊚** VME64x, VME64 or cPCI<sup>®</sup> compatible

- Mil 461-D, E for shock/vibration, EMI/RFI

- O CE and FCC class B, Part 15

- Many power options

790 Chassis

792 Chassis

### **VECTOR SPECIALIZES IN:**

UNPARALLED FACTORY SUPPORT

CUSTOM CONFIGURATIONS

ed SHORTER LEAD TIMES

Series 445, Modified Full EMI/RFI

(800)423-5659 www.vectorelect.com

NATO III

### Field Intelligence

### MIL-STD-1553's longevity is well deserved

After almost 40 years of deployment, the MIL-STD-1553 databus protocol still holds a strong position on military platforms. How can a technology that old still have a place in mission-critical systems when so many newer databus protocols have appeared on the scene? Real-time deterministic capabilities and reliability, coupled with a vast installed base, have ensured 1553's ubiquity. Current and future military platforms will engage newer databus protocols, but 1553 will still be around for quite some time.

### The evolution of 1553

In 1968, the Society of Automotive Engineers (SAE), a technical body of military and industrial members, established a subcommittee to define a serial data bus to meet the needs of the military avionics community. Several years of military and government reviews and changes led to the August 1973 release of MIL-STD-1553, with the U.S. Air Force's F-16 as the initial standard's primary user.

After some "real world" experience, program managers soon realized that further definitions and additional capabilities to the standard were needed. The SAE group spent three years of concentrated effort to produce the follow-on standard, MIL-STD-1553B, which was released in 1978. At that point, the government decided to freeze the standard at the "B" level to allow component manufacturers to develop products that could be immediately deployed. And today, the venerable 1553B standard is still in use.

### A look inside MIL-STD-1553

The MIL-STD-1553 time division multiplexing data bus is the most ubiquitous military data bus today, used in platforms where data integrity and system reliability are critical. MIL-STD-1553 defines a method that permits digital signal communications along a common databus network with the real-time characteristics of a direct cable connection. It saves the weight and expense of miles of individual cables used to connect subsystems such as aircraft control surfaces and navigation controls.

By defining the standards for the functional, mechanical, and electrical characteristics of the serial data bus commonly used in the avionics of military aircraft, MIL-STD-1553 has been utilized to integrate computers into aircraft platforms and provide greatly enhanced reliability and performance while reducing costs.

### MIL-STD-1553 applications

Since its inception, MIL-STD-1553 has found numerous applications. Notice 2 to the standard has removed all references to aircraft or airborne so as to not limit its use to aircraft platforms.

### Space and military venues

Although the standard has been applied to satellites and payloads within the space shuttle and International Space Station realms, its military applications are the most numerous and far ranging. It is employed on large transports, submarines, aircraft refuelers, bombers, tactical fighters, and helicopters. It is even contained within missiles and serves in some cases as the primary interface between the aircraft and missile. The U.S. Navy has applied the data bus to accommodate both surface and subsurface ships. And the U.S. Army utilizes 1553 in its helicopters, tanks, and howitzers.

Additionally, the central role that the 1553 standard plays in weapons delivery will remain strong, even with the latest fighters. For example, the Joint Strike Fighter F-35's avionics data bus is not limited to MIL-STD-1553B, but also includes IEEE1394B Firewire and Fibre Channel for use in flight control and data display.

Because of its longevity, MIL-STD-1553 products, reference guides, and tutorials are readily available. Rugged COTS MIL-STD-1553 interface hardware, such as the RXMC1553 XMC.0 Mezzanine Card from GE Intelligent Platforms, are also building the 1553 ecosystem. Depicted in Figure 1, the XMC combines high-speed encoding and decoding and intelligent protocol processing with advanced Application Programming Interface (API) software that reduces 1553 application development time.

Figure 1 | The RXMC1553 XMC.0 Mezzanine Card from GE Intelligent Platforms

### Transportation and government

MIL-STD-1553 products have even found their way into transportation applications such as San Francisco's Bay Area Rapid Transit (BART) system. Other non-military applications include nuclear reactors and manufacturing production lines.

Meanwhile, government adoption of MIL-STD-1553B includes acceptance and implementation by the North Atlantic Treaty Organization (NATO) and many foreign governments. The UK has issued Def Stan 00-18 (Part 2), and NATO has published STANAG 3838 AVS, both of which are versions of MIL-STD-1553B.

### Looking ahead: Is MIL-STD-1553 a panacea?

Higher-performance data bus technologies such as IEEE1394B Firewire, Fibre Channel, and GbE are moving into areas once solely occupied by MIL-STD-1553. Today's modern aircraft use a mix of highperformance data buses and 1553. These newer technologies bring higher network speeds than 1553's 1 Mbps and are well suited for high-bandwidth applications such as video transmission and sensor displays, coexisting with MIL-STD-1553 but not supplanting it completely.

The 1553 protocol's extensive use in platforms and applications with service lives spanning decades will ensure the standard will be supported and employed by the military, government, transportation, and commercial sectors for years to come.

To learn more, e-mail Duncan at duncan\_young1@sky.com.

# Mil Tech Insider

# I/O mezzanines for FPGA-based reconfigurable computing

By Steve Edwards Which mezzanine format - the PCI Mezzanine Card (PMC), Switched Mezzanine Card (XMC), or FPGA Mezzanine Card (FMC) – is best for reconfigurable FPGA-based computing applications? The answer depends on design issues such as application details, perception of risk, development timeline, XMC, and FMC modules. and personal preference. FPGAs are ideal for high-bandwidth I/O applications because they connect directly to I/O devices to

Any of these three mezzanine approaches should be compared with monolithic board technology, for example, a single Printing Wiring Board (PWB) with all FPGA functionality onboard. While representing the least flexible and possibly most costly approach, the monolithic card usually provides the best technical option because it does not have the restrictions imposed by segmenting the design, such as the number of connector I/O pins to the mezzanine. However, depending on application requirements, it is probable that rugged FPGA I/O will be served by the PMC, XMC, or FMC open standards.

ensure low latency and support high-speed front-end DSP.

### PMC and XMC with FPGAs?

PCI-X (PMC) or PCI Express (XMC) latency is typically in the order of 1 to 2 microseconds and delivers bandwidths of just a few GBps, which is sufficient for some of the more demanding applications, but not for all. For some FPGA applications, PCI, PCI-X, PCI Express, and Serial RapidIO can actually dilute the advantages of using FPGAs, which excel with parallel streaming dataflows. The FMC module, similar in height and width to a PMC but approximately half the length, is designed to carry only the I/O devices and connect them directly to the FPGA device on the host board. This approach enables interface optimization among the I/Os, and the FPGA and also delivers a reduction in real estate, cost, latency, and power while boosting bandwidth.

FPGAs are ideal for high-bandwidth, high-resolution I/O because of the many I/O connections provided. This is especially true if high-speed memory is required to buffer the input or output data streams. These applications usually demand the largest FPGA packages with the most available I/O pins. Because these devices tend to be large, measuring 35 x 35 mm or more, they can violate the PMC or XMC specifications' "no go" area across the module's middle where components are banned. This restricted area forms part of the card's primary thermal interface for conductioncooled cards and serves as a mechanical fixing area to marry with stiffening bars on the host. The result: Using large FPGA packages on PMC or XMC cards can encroach on the real estate where the designer would ideally want I/O devices placed.

### Relative sizes of PMC/XMC and FMC modules

The FMC has a simplified power requirement that frees up valuable module real estate for additional I/O. FMC measures only about a half the PWB area of a PMC or XMC, but an FMC can often provide greater I/O functionality compared to PMCs

and XMCs because of the PMC and XMC "no go" restriction mentioned earlier. The useful space for I/O devices on PMC/ XMC can sometimes end up only a quarter of the overall real estate of the XMC. Figure 1 shows the relative sizes of PMC,

Figure 1 | The relative sizes of PMC, XMC, and FMC modules

### Rugged PMC and XMC versus FMC cooling

FMCs also simplify cooling challenges, especially on small form factor cards. When plugged onto a 3U host card such as 3U VPX, a PMC or XMC covers the majority of the host's real estate. Any hot devices on the host will be located beneath the XMC, seriously affecting cooling. Furthermore, an XMC mezzanine's devices are located facing the host, which places the heat generating devices opposite those on the host and increases the cooling problem. In 6U designs, the situation is not much better. While some of the 6U host's real estate is not covered by the mezzanine card(s), the thermal paths to either the cooling air inlet or cold wall interface are longer.

Because of FMC's smaller size, less of the host board is covered by the mezzanine. Appropriate FMC host design allows for suitable heat sinks to be implemented in the areas not restricted by mezzanine placement. And since only the I/O devices, not the FPGA, are on the module, the FMC is easier to cool. The FMC specification limits the power dissipation of a single-width module to 10 W.

### **FMC** complements **PMC** and **XMC**

While FMCs were designed for front-panel I/O, Curtiss-Wright Controls Embedded Computing (CWCEC) addresses this limitation with right-angle connectors and a specially designed strain-relief bracket to secure the connectors and minimize vibration damage to delicate connectors. This has been implemented on the 3U FPE320 board and is designed into or planned for all of the company's future FMC-based products.

FMC does not compete with PMC or XMC, but rather complements it, specifically for high-bandwidth, low-latency applications. Depending on the application, it is likely that rugged FPGA I/O will be serviced by one of these open standards. Where they cannot meet the requirements, the monolithic approach provides the safety net. Determining which approach works best will depend on application specifics.

To learn more, e-mail Steve at Steve. Edwards@curtisswright.com.

# We create space...

Microsemi's lean microelectronic solutions increase board density, solve component incompatibilities, reduce design complexity, and extend product life and environmental performance in military applications. We offer turnkey design, assembly and test of custom multi-chip solutions, and a wide range of standard military off-the-shelf space-saving solutions.

Expand the possibilities; visit www.whiteedc.com/spacesaving.

Our SLC NAND flash SSD BGA provides big features in a miniaturized package, freeing up precious board space. It is engineered specifically for the defense market, designed to ensure data reliability in mission critical rugged and mobile systems. Constructed using a 32-bit RISC processor as its core storage controller, this SSD is available in 4, 8 and 16 GByte densities.

Learn more at www.whiteedc.com/ssd.

602.437.1520 TEL | 602.437.9120 FAX

Graphics represent a challenging area for managing software obsolescence. Most applications that render to the screen or manage a user interface make use of low-level driver calls, such as OpenGL, and extensive User Interface (UI) libraries such as X-Windows or other UI libraries. Deploying these software applications on new platforms when technology insertion is needed because of performance requirements changes or obsolescence is challenging. However, a methodology whereby graphics and UI interfaces can be abstracted without sacrificing performance or flexibility is vastly extending the useful life of legacy software when technology insertion is required.

### Why are graphics and UI a legacy problem?

User interface and graphics software represents a significant proportion of any software system that requires user interactions. In military systems, User Interfaces (UIs) range from real-time embedded displays through extensive digital map and geospatial

Ruggedized 3U Fibre **Channel RAID System** Phoenix International designs and builds rugged COTS Data Storage Systems that plug and play in any application -- from Multi-Terabyte Fibre Channel RAID and Storage Area Network configurations to plug-in Solid State Disk Drive VME/cPCI Storage Modules. **Military** Operational altitude to 45,000 feet Operational Temperature -20° to +60°C · Redundant, hot swap components/FRU's · 40Hz to 440Hz, 90/240 VAC Input Operation See us at: www.phenxint.com or contact us at: 714-283-4800 • info@phenxint.com An AS 9100 / ISO 9001: 2000 Certified Service Disabled Veteran Owned Small Business We Put the State of the Art to Work sm

C4ISR applications. User interface software is unique in that it is highly visible to the computer user while at the same time interfacing directly to graphics hardware through driver calls. Such driver calls include those provided by standards such as OpenGL or by APIs such as rendering libraries provided for a radar processor to draw reticles or text.

In addition, user interface software is highly dependent on operating system constructs such as a windows manager (for example, X-Windows), often also used to provide 2D graphics capabilities. Many times the chief impediment to software portability is in the UI and graphics area. This is even more true when trying to manage legacy software migration to systems that require technology insertion, such as replacement of obsolete graphics chips.

Many tools and methods have been developed during the years to aid in making UI and graphics applications more portable and resistant to obsolescence. For instance, many popular software tools and libraries that abstract the interface to the graphics hardware are available for developers' use. These tools might employ code generation (example: Presagis VAPS) or pass graphics rendering calls through an abstraction library (example: Nokia QT).

These development tools are very beneficial, but they do not help much with a legacy code base that has extensive dependence on graphics calls. In many cases, technology insertion requires investment in new graphics drivers or window management software to match legacy software's API needs. The API calls required by the legacy application are implemented in the hardware device driver. In practice, this means that hardware evolution is slowed, and that hardware capabilities do not evolve as they should. For military systems, sadly, it also often means that developers cannot take advantage of new technologies that would greatly benefit the system, such as low-power, low-cost computing platforms that are revolutionizing mobile computing. Industry standard groups such as Khronos (www.khronos.org) have paved the way for new, low-power graphics and UI systems through defining and supporting new standards such as OpenGL ES for embedded graphics. However, these standards are designed to enable UIs and rich graphics experience with drastically reduced APIs and embedded driver sizes. Few would argue that they deliver rich, useful user interfaces, but legacy software cannot take advantage because it was not written to support these new, streamlined APIs.

Simply put, graphics software obsolescence is leaving military systems stuck in the past. This means that soldiers, sailors, and airmen are using computers that cost more and consume more power than they need to, and often deliver substandard operation. In addition, new technologies that make smartphones, TabletPCs, and automobile computers ever more user-friendly and useful cannot find their way to military embedded systems.

### New software approaches

Several approaches exist to bring legacy graphics software applications onto these new hardware platforms. One approach that offers much promise is to leverage the concept of virtualization and apply this to graphics and UI systems. Using this approach, graphics-rendering commands – whether legacy APIs, 2D window-management commands, or 3D rendering - can be implemented through a virtualization mechanism similar to those used for other OS and device interfaces. The main challenge in implementing such a scheme lies in preserving the performance and real-time interface to the hardware and graphics resources while still supporting the needed APIs. For this reason, a good virtualization solution must be built from the device-driver level to ensure success. A "hybrid" between a traditional driver and a virtualized one is necessary.

Such a "hybrid" approach can offer high-performance, divergent back-end implementations for new devices in addition to frontend APIs that legacy applications expect. Graphics resources and commands must be marshaled by this layer to deliver real-time performance. The virtualization layer must be prepared to manage graphics resource memory and virtualized device interfaces such as windows. It must also be ready to perform seamless lowoverhead API conversions as required.

### **Embracing the future**

The best approach for managing obsolescence in graphics and UI applications is to design and develop for it up front, by choosing a development strategy and tools that attempt to "future proof" an application and by adhering to relevant standards such as those offered by Khronos. When this is not possible, a virtualization

Simply put, graphics software obsolescence is leaving military systems stuck in the past. This means that soldiers, sailors, and airmen are using computers that cost more and consume more power than they need to, and often deliver substandard operation.

strategy, or "hybrid" device driver, can offer a promising alternative. Work remains to be done, but graphics virtualization is a new and promising area. It offers a way forward to bring legacy military graphics systems into the new computing world vigorously charted by smartphones, TabletPCs, and the devices that are changing everyday lives.

Mark Snyder is Vice President of Product Marketing for ALT Software. He has been responsible for many innovations in user interface and real-time computer graphics software architectures and tool chains during his 25-year career working at Quantum3D, Honeywell International, and the U.S. Air Force. He can be contacted at msnyder@altsoftware.com.

# Daily Briefing: News Snippets

By Sharon Hess, Assistant Managing Editor

www.mil-embedded.com/dailybriefing

### NASA's TDRS gets more modern

NASA's Tracking Data and Relay Satellite (TDRS) constellation is about to get a facelift, per a recent contract awarded by NASA to General Dynamics C4 Systems. The IDIQ contract, with an option-inclusive potential value of \$642.2 million, stipulates that General Dynamics modernizes TDRS's network and ground system. Specifically, a new ground-system architecture will be implemented to perpetuate tracking coverage and spaceto-ground telecommunications for near-Earth and low-Earth missions. Because the TDRS network supports the entire gamut of NASA human flight and scientific space missions, including the International Space Station and Hubble Space Telescope (Figure 1), integration will be a strong focus to avoid interruption of present space network operations. Contract work is slated through June 2017. The TDRS modernization falls under the NASA Space Network Ground Segment Sustainment (SGSS) project umbrella.

Figure 1 | Hubble Space Telescope image courtesy of NASA/hubblesite.org

### "GMTI radar aboard the WASP UAV?"

... That is the question on DARPA officials' minds these days, thus the agency recently commissioned OEwaves to find out just whether GMTI onboard the WASP UAV was feasible - or not. OEwaves conducted the study utilizing both conventional RF technologies and the company's proprietary microwave photonics technologies. OEwaves demonstrated, via Whispering Gallery Mode (WGM) optical resonator technology, that a GMTIparameter-resembling transmit/receive capability was possible – and compatible with the WASP's power envelope, weight, and size. The study's findings are anticipated for use in an unnamed future DARPA project. Meanwhile, OEwaves' crystalline WGM optical resonator technology, in addition to the photodetector and miniature resonator's small bandwidth, is touted to deliver "one-step photonic mixing," as opposed to traditional super heterodyne receivers that require several steps in filtering and mixing.

### **DARPA** project aims to reduce surveillance woes

Sorting through copious amounts of surveillance video data can prove a daunting task – and one that typically results in many false positives – but one that can be managed more effectively. Case in point: DARPA and Kitware recently signed a nearly \$14 million contract stipulating that Kitware develops software that can interactively and automatically glean actionable intelligence derived from Wide Area Motion Imagery (WAMI) video of rural, suburban, and urban areas. The software aims to thwart the stops and occlusions that can fragment tracks, particularly in urban locales. The problem solver: algorithms that can integrate local events, identify threats, then conduct forensic analysis. The algorithms will then spawn the Persistent Stare Exploitation and Analysis System (PerSEAS) software prototype, which will utilize context, normalcy, and activity models to provide operator ease in identifying new intelligence. To reduce the frequency of false alarms, the models are relationship-based to make suspicious anomalies more evident versus benign events. The contract's Phase I research is slated for completion in 2012.

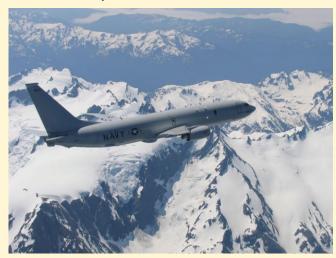

### Raytheon APY-10 goes international

A recent contract between Boeing and Raytheon Company serves as impetus for development of the first international version of Raytheon's APY-10 surveillance radar. The international APY-10 iteration is slated for installation on Boeing's in-development P-8I maritime surveillance aircraft, the P-8A's first international variant procured by the Indian Navy. APY-10's mission is to provide actionable, accurate intelligence for ISR and anti-surface and anti-submarine warfare, come rain or shine. Raytheon is additionally working to fulfill its U.S. Navy/Boeing contract to render six APY-10s for the P-8A (Figure 2), four of which were already delivered.

Figure 2 | P-8A Poseidon, photo courtesy of Boeing

### Simulation eases training at Whidbey Island

Tactical training just got a whole lot easier, not to mention safer, for EA-18G Growler and EA-6B Prowler (Figure 3) operators stationed at Whidbey Island, the locale the entire host of the aforementioned aircraft attack squadrons call "home." The facilitator: a recent contract between the U.S. Navy and Tactical Communications Group (TCG), specifying that TCG's Ground Tactical Data Link System (GTS) tactical training and simulation system be used for rendering realistic tactical training for ground operational personnel and pilots. GTS, geared for terrestrial TDL networks, enables military air operators to establish live tactical data link networks and serves to automate and simplify Link 16 network entry processes. Combat scenarios are also realistically rendered via dual-screen display of both the cockpit and the full tactical situation at hand, to increase situational awareness capabilities.

Figure 3 | Training just got a whole lot easier for EA-6B Prowler (pictured) and EA-18G Growler pilots and operators at Whidbey Island. U.S. Navy photo by Mass Communication Specialist 2nd Class John Philip Wagner Jr.

### Harris Corp.'s Falcon radios travel to Asia

Harris Corporation's Falcon radios are about to embark on a very long voyage: The company has reported multiple orders, amounting to \$99 million, from an unnamed military customer in Asia. Specifically, the RF-7800S, RF-7800V, RF-7800M, RF-5800H, and RF-7800W Falcon II and Falcon III software-defined tactical radio systems will form the backbone of a multilevel C4I system's next phase, to be completed by Harris. Falcon radios are suited for vehicular, handheld, or manpack radios and additionally meet the U.S. military's JTRS specifications for global netcentricity. The RF-7800S wearable secure radio affords soldier communications over distances exceeding 2 km; the RF-7800V renders data connectivity up to 192 Kbps; the RF-7800M wideband tactical radio offers networked comms over the 30 MHz to 2 GHz frequency range; RF-5800H is a High Frequency (HF) radio providing Automatic Link Establishment (3G-ALE); and RF-7800W is a wireless IP networking radio providing secure broadband connectivity.

For consideration in Daily Briefings, submit your press releases at http://submit.opensystemsmedia.com. Submission does not guarantee inclusion.

Figure 4 | The HULC exoskeleton will soon undergo \$1 million worth of testing. Lockheed Martin photo

### **Lockheed Martin's HULC flexes its**

Perhaps similar to its sound-alike namesake, Lockheed Martin's HULC will soon get an opportunity for muscle flexing in the form of testing – per a recent \$1.1 million contract between the company and the U.S. Army Natick Soldier Center. The contract affords testing of the upgraded HULC system, a hydraulicactuated anthropomorphic exoskeleton featuring robotic legs powered by an onboard microcomputer and optimized control software to facilitate wearer-synchronized exoskeleton movement. HULC is designed to ease dismounted soldiers' injuries and fatigue resulting from carrying heavy loads of combat equipment. HULC is battery powered and can provide crawls, deep squats, and upper-body lifting, with virtually no operator exertion. Testing will comprise HULC's effects on operator performance, soldier energy expenditures during HULC use, and operator learning speeds when moving around or carrying different loads.

### **USMC "System of Systems" garners** upgrades

The Marine Corps Systems Command in Quantico, Va., and L-3 Communications, Nova Engineering, Inc. recently put pen to paper for upgrade/repairs, equipment systems, and program management pertaining to the Tactical Remote Sensor System (TRSS) System of Systems (SoS). The IDIQ contract is dollar-based, as opposed to quantity-based, with a ceiling of \$52,781,000. TRSS SoS is designed to provide remote activity monitoring close to or in a specified locale, and in all weather conditions (Figure 5). The first delivery order on contract is anticipated at \$10,854,132, and work will commence in Cincinnati, Ohio. Meanwhile, contract completion is scheduled for July 2015.

Figure 5 | The Tactical Remote Sensor System (TRSS) System of Systems (SoS) will soon be getting upgrades, repairs, equipment systems, and program management per a recent contract. U.S. Air Force photo by Senior Airman Alexandra Sandoval

# RFID and asset authentication: Enabling true security measures

By Neil Mitchell

Tracking military wares is integral to efficient logistics, cost savings, and most importantly, security. RFID tags are often used for security purposes, but the results can be disastrous when RFID tampering occurs. However, there is a remedy.

Streamlining logistics, compliance demands, and tuning processes to increase cost savings, efficiencies, and revenues is only part of the overall benefits RFID can deliver. In areas where security is of great importance, authentication is a piece of the RFID system that is often overlooked. Without the proper technologies in place, certainty that an RFID tag is tracking the item it is intended to track just cannot be guaranteed.

For instance, what if an RFID tag separates from its asset or is applied to another object or container? Or, worse yet, what if the RFID tag remains on a container but the contents of that container are removed or replaced? In either case, the accuracy of the RFID system is compromised.

These are just a few examples of why it is critical to maintain a one-to-one relationship between the tag and the asset. Without this, the benefits of RFID will not be fully realized. Physical tamper protection of the RFID tag itself is the solution to this issue (Figure 1). If a tag is tampered with, the tag is permanently altered or destroyed.

If implemented correctly, the RFID tag can have the option to secure assets by serving as a seal. With special consideration given to the tag and reader location, as well as the need for inclusion of other electronics, the ability to read the tag confirms the authenticity and wholesomeness of the asset.

Figure 1 I A tamper-evident RFID tag in the process of being destroyed during a tamper event

An RFID system without these types of physical tamper-evident indicating tags is an incomplete system that invites fraud and compromises security.

Neil Mitchell, VP Marketing for MIKOH Corporation Limited, delivers expertise in security solutions for automatic vehicle identification, secure asset tracking, digital marking, and secure network online identification. Over the past 20+ years, he has worked for STMicroelectronics, NXP Semiconductors, and Xceive.

Mitchell can be contacted at nmitchell@mikoh.com.

MIKOH Corporation Limited www.MIKOH.com

# A new era, a new ESC New tracks. New courses. New focus. Entering into its 21st year in Boston, ESC brings together systems architects, design engineers, suppliers, analysts, and media from across the globe. With cutting edge product demonstrations, visionary keynotes, and hundreds of essential training classes, ESC is the ideal conference for the embedded design community to learn, collaborate, and recognize excellence.

### ESC Boston 2010 Tracks Include:

- Aerospace and Military

- Designing with Open Source Software, including Linux and Android

- Developing for Windows Embedded

- Graphics, Display and Lighting

- Industrial, Automation, and Robotics

- Medical

- Multicore and Virtualization

- Multimedia and Signal Processing

- Networking, Connectivity, and Embedded Internet

- Programmable Logic

- Project Management

- Real Time System Development

- Safety and Security

- Software Debugging Techniques

- Systems Integration and Test

Start your own personal development at ESC 2010. You can't afford to miss it. Expo Floor Access is FREE!

Boston, MA

Hynes Convention Center

Conference: September 20-23, 2010

Expo: September 21-22, 2010

Register Today. www.embedded.com/boston

Confronted by rapidly evolving threats, the DoD can look to COTS-based rapid prototyping of cost-effective, high-performance Digital Signal Processing systems to meet stringent Size, Weight, and Power (SWaP) constraints and mission objectives for Intelligence, Surveillance, and Reconnaissance (ISR) operations.

Modern warfare is forcing the U.S. military to quickly adapt to rapidly evolving asymmetric threats in an effort to maintain U.S. military tactical situational awareness. However, the traditional dependence on custom, stove-piped Digital Signal Processing (DSP) system implementations consisting of Application-Specific Integrated Circuits (ASICs) and Application-Specific Standard Products (ASSPs) is restricting the agility of U.S. military Intelligence, Surveillance, and Reconnaissance (ISR) operations.

To address these limitations and volatile threats, the U.S. DoD is increasingly funding ISR Quick Reaction Capability (QRC). However, this new acquisition model challenges tactical ISR system developers to rapidly prototype cost-effective, highperformance DSP systems while meeting stringent Size, Weight, and Power (SWaP) program requirements. To satisfy these demands, a novel rapid prototyping methodology leverages COTS hardware/software signal processing technology and cost modeling to close the data collection/analysis gap, thwart the limits of traditional ISR design methodologies, and reduce development time and expense while meeting challenging ISR mission requirements.

### Closing the collection-analysis gap in ISR mission scenarios

The increased demand for ISR capabilities has led to an exponential increase in data collection capacity over the past few years and will continue to do so for the foreseeable future. However, ISR data Processing, Exploitation, and Dissemination (PED) processes have only improved linearly over the same period, leaving a critical gap between collection and analysis capabilities. To close the collection-analysis gap, the DoD needs high-performance DSP-based ISR systems that enable automated, real-time processing of massive amounts of data and dissemination of actionable intelligence directly to the warfighter in the field.

High-end ISR applications such as real-time, automated PED push the limits of state-of-the-art COTS DSP technology. Throughput requirements may exceed tens of tera-ops/s. New many-core Graphics Processing Unit (GPU) and General Purpose Processor (GPP) architectures appear to be theoretically capable of satisfying such high-end performance requirements. It is, however, an extremely difficult task to develop parallel software algorithms to fully exploit more than only a fraction of the peak performance of many-core architectures.

The rapid prototyping of cost-effective system implementations that meet such extreme performance requirements under severe SWaP constraints is a monumental task. Detailed trade-off analysis and extensive architectural exploration during the frontend design process are critical to accomplishing this goal. Table 1 shows a comparison of many-core GPU, multi/many-core GPP, multi-core DSP, and Field Programmable Gate Array (FPGA) technologies with respect to processor-specific software tool availability, processor peak throughput, and power efficiency. The maturity of processor-specific software development tools has a significant impact on system development effort, cost, and schedule. System developers must optimally trade off the maturity of software tool support with hardware performance and power efficiency to meet high-end ISR application requirements.

### Limitations of traditional ISR design methodologies

Most of today's ISR systems follow the "waterfall" development method, which dictates a sequential process. Current waterfalltype design processes for high-performance ISR systems impose a number of limitations, including:

- Limited architectural exploration

- Lengthy prototyping times

- High cost of design

- Lack of systematic hardware/software reuse

- In-cycle hardware fabrication and testing

|                                      | Processor-Specific SW Development Tool Availability                                                                                                                                                   |                                                                               |                      | Performance and Power Efficiency Parameters                                   |                                       |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------|---------------------------------------|--|

| Processor                            | Software Tool Usage Description                                                                                                                                                                       | SW Tool Usage Rating                                                          | Effort<br>Multiplier | Peak Throughput<br>per chip                                                   | Power Efficiency                      |  |

| Tilera TILE64<br>Many-core GPP       | ANSI standard C / C++ compiler;<br>profiling and debugging tools for<br>multi-core programming; SMP Linux;<br>multi-core component libraries for<br>interprocessor core communication                 | Nominal<br>(Lacks DSP software<br>library support)                            | 1.0                  | <u>Fixed Point</u><br>443 GOPS                                                | 22 W<br>(all cores active at 700 MHz) |  |

| NVIDIA Tesla C2050<br>Many-core GPU  | C / C++ / Fortran compiler; CUDA-GDB<br>debugger; CUDA Visual Profiler; OpenCL<br>Visual Profiler; GPU-accelerated BLAS<br>library; GPU-accelerated FFT library                                       | High<br>(Mature tool and<br>library support for DSP<br>parallel programming)  | 0.86                 | Single Precision Float<br>1.03 TFLOPS<br>Double Precision Float<br>515 GFLOPS | 247 W TDP                             |  |

| Intel Core i7 -920<br>Multi-core GPP | C / C++ / Fortran compiler; Math<br>Kernel Library; integrated performance<br>primitives for multimedia, data process-<br>ing and communications; threading<br>building blocks; performance analyzers | Very High<br>(Very mature and well<br>integrated tools)                       | 0.72                 | Single Precision Float<br>85 GFLOPS                                           | 130 W TDP                             |  |

| TMS320C6472<br>Multi-core DSP        | Code Composer Studio IDE; data visualization kit; math library; signal processing library; image library; floating point emulation                                                                    | Nominal<br>(Good library support;<br>basic multi-core<br>programming support) | 1.0                  | Fixed Point<br>256 GMACS<br>Single Precision Float<br>128 GFLOPS              | 5.4 W TDP                             |  |

| Altera Stratix V<br>FPGA             | Quartus II design software including support for planning, simulation, timing analysis, debugging, verification, and synthesis                                                                        | Very Low<br>(Time-intensive<br>verification and<br>validation process)        | 1.24                 | Fixed Point<br>1840 GMACS<br>Single Precision Float<br>1TFLOPS                | 110 W TDP                             |  |

Table 1 | System developers must optimally trade off the maturity of software tool support with hardware performance and power efficiency to meet high-end ISR application requirements.

Most design automation activities have focused on leveraging tool support for detailed system behavioral design, as opposed to early architecture design where much of the system cost is committed. Current industrial practice predominately relies upon designer experience to select system architectures and allocate algorithm functionality. Furthermore, for fully customized ISR systems, hardware and software subsystems are not integrated until after hardware is fabricated, making design errors very costly.

### **Grounded innovation: COTS-based rapid prototyping**

The increased frequency of ISR system development cost overruns and schedule delays has compelled the DoD acquisition community to launch numerous initiatives that encourage the contractor community to better leverage COTS DSP hardware boards and system components.

In COTS hardware-based systems, the time and cost of software development can, however, dominate the schedule and budget. Parametric studies based on historical project data show that designing and testing embedded software is particularly difficult if margins of slack for processor and memory resources are too restrictive. Severe resource constraints may prohibit embedded software developers from leveraging high-level programming tools, thereby requiring direct interaction with the hardware and/or operating system to optimize code to meet system requirements.

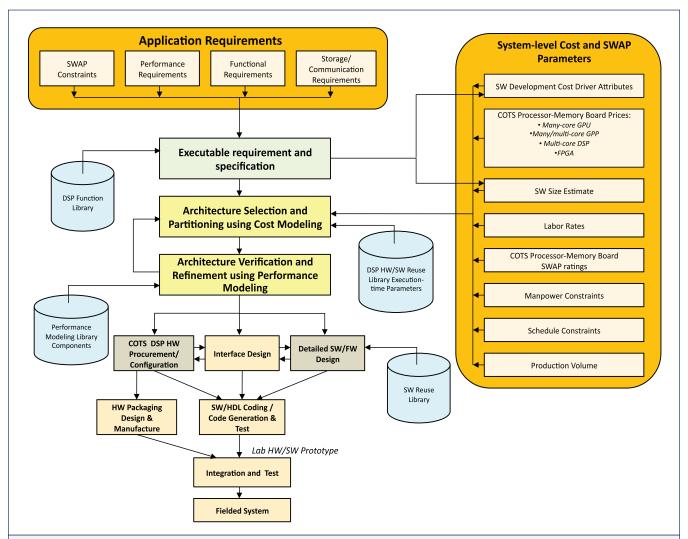

One innovative solution garnering attention in the industry is a rapid prototyping methodology that exploits the use of COTS hardware/software signal processing technologies and

cost modeling to achieve significant reductions in total ISR system cost and development time. This approach leverages a COTS library-based optimization framework that includes tradeoffs in throughput, hardware/software development costs, and schedule, procurement costs, and SWaP. This rapid prototyping methodology maximizes system architectural exploration in the front-end design process. The resulting solutions are costeffective DSP embedded systems that exploit the flexibility of many-core GPU, multi/many-core GPP, multi-core DSP, and/or FPGA technologies, while satisfying stringent SWaP constraints dictated by mission objectives.

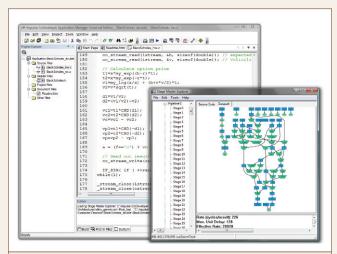

Figure 1 illustrates the COTS-based rapid DSP system prototyping methodology. The process starts by translating written system requirements into executable requirements and specifications using signal processing libraries and integrated Graphical User Interface (GUI) toolkits such as those available in MATLAB. The executable requirements and specifications provide an early prototype to the customer to validate original requirements and to remove ambiguities. This feedback allows for receiving any requirement alterations as early as possible, which is critical to minimizing the high cost of requirements creep, one of the most common risks in software projects.

After the validation of system requirements, system-level cost parameters, application requirements, and performance statistics, these components feed the architecture selection and partitioning optimization process. System developers can use parametric cost models, such as COCOMO II, to drive the architecture trade-off analysis, producing hardware/software architectural candidates that minimize total system cost and development time. The cost parameters include: software cost driver attributes (size, product, platform, personnel, and project), COTS hardware procurement costs, product deployment deadlines, schedule constraints, and labor costs and constraints. Application requirements include SWaP, environmental, precedence, and real-time constraints, as well as functional, memory, and communication requirements. Performance statistics consist of benchmark time measurements of DSP primitives (for example, fast Fourier transform) executing on the DSP processor boards (for example, many-core GPU, multi/many-core GPP, multi-core DSP, FPGA) contained in the reuse library.

System developers can then simulate the resulting architectural candidates using dynamic performance modeling tools, such as Simulink, to verify that an architecture meets systemlevel requirements. After performance modeling, the system

Figure 1 | The COTS-based rapid prototyping methodology prioritizes both application requirements and cost modeling, critical to minimizing the high cost of requirements creep.

architect feeds communication overhead parameters such as communication queuing delays and bottlenecks back to the architecture selection stage for refinement. The methodology produces new architecture candidates with the updated model parameters and repeats the process until the architecture meets performance requirements and no longer changes between successive iterations.

The refined hardware/software architectural candidate moves on to the detailed architecture design stage for detailed software and/or firmware design, hardware/software interface design, and COTS procurement. Depending on the COTS DSP hardware platform and architecture selected, the DSP software and/ or firmware design process heavily leverages reusable libraries developed in previous projects. The cost of assessing, selecting, assimilating, and modifying the reusable component must also be minimized to significantly reduce software development expense and time. System designers can refine the candidate architecture's performance model and executable signal processing algorithm specifications to permit automatic code generation into the C programming language or a hardware description language. To enable the use of automated code generation tools, sufficient hardware resource slack margins and high-level software tool support must exist for the target DSP board architecture.

The high-level virtual prototypes of the system allow the system designer to catch hardware/software integration errors early in the design process. This approach allows for low-level performance limitations to be identified and corrected before costly hardware packaging assembly and field testing.

### Rapid prototyping helps ISR systems keep pace

Traditional DSP implementations for ISR systems can no longer keep pace with modern warfare. System developers need a rapid prototyping methodology that exploits the use of COTS hardware/ software signal processing technologies and cost modeling to achieve significant reductions in total ISR system cost and development time. IvySys Technologies' Real-Time Intelligence Analysis methodology fully leverages this COTS-based rapid prototyping approach. The front-end design process is automated by incorporating software cost and development time models. The design optimization process reduces development time and cost by as much as a factor of four. The IvySys COTS-based rapid prototyping methodology enables the DoD and intelligence community to quickly adapt to rapidly evolving asymmetric threats and to thereby maintain U.S. tactical situational awareness.

Dr. James A. DeBardelaben is the President and CEO of IvvSvs Technologies, LLC. Prior to founding IvySys, he worked as an expert consultant in Special Operations ISR, real-time embedded software, and tactical distributed systems and networking. James received a Ph.D. in Electrical and Computer Engineering from the Georgia Institute of

Technology, an M.S.E in Computer Engineering from Princeton University, and a B.S. in Electrical Engineering with honors from Brown University. He may be reached at jd@ivysys.com.

> IvySys Technologies, LLC 703-414-5665 • www.ivysys.com

### **NEW!** Larger FPGA for PCIe x8 FPGA board / accelerator

- Giant configurable FPGA (XC5VSX240T)

- PowerPC 440 processing

- User-available DDR2

- 1.2 to 1.6 GB/s DMA

- Standard connector for mezzanine boards

- · Windows, Linux, Solaris

### NEW! MIL-STD-1553B for PCle

- 1 bus controller

- 1 bus monitor

- 31 remote terminals

- Windows, Linux, Solaris

www.edt.com

# Special: UAVs step up to the front line

Network-centricity and recent advances in high-speed serial fabric technologies, along with legacy device bridging methodologies, enable highly flexible UAV system architectures to meet the rapidly changing demands of the 21st century battlefield, while shortening time-to-market and mitigating risks.

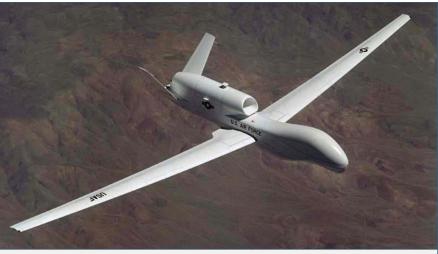

The roles of Unmanned Aerial Vehicles (UAVs), like the Global Hawk UAV shown in Figure 1, are expanding. As UAVs' strategical and tactical mission capabilities continue to expand, there is an ever-increasing need for highly reliable, high-performance electronic systems that can support high-bandwidth network connectivity within the platform - and from the platform to the Command and Control infrastructure. UAVs are increasingly becoming networked systems; they are one element of the entire Unmanned Aircraft System (UAS) that communicates and shares mission-critical payload and sensor information with other elements such as ground control stations and ground/ remote terminals to provide a common operating picture.

This migration from platform-centric to a network-centric systems approach poses new challenges that are met by the use of open architectures. Formerly, UAVs adopted platform-centric architectures that relied on proprietary interfaces. Many of these design concerns can now be overcome by ruggedizing commercial electronics, enabling subsystem technologies containing COTS components and allowing faster time-to-market. The result is rapid battlefield deployment of the newest technologies.

Advances in open standards performance, such as VPX high-speed serial fabrics, along with the ability to bridge legacy devices, make it possible to develop scalable and interoperable networkcentric subsystems at significantly lower development and logistical risks.

Figure 1 | The demand for UAV technology is ever-increasing, and the Global Hawk is one example of such technology.

### **Network-centricity eases** interfacing

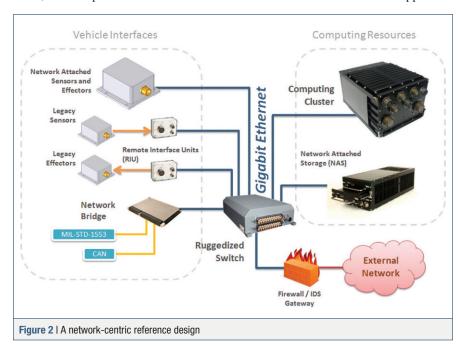

Net-centric architecture enables the UAV system designer to standardize the interface between the computing elements and the interface elements. For example, a COTS SBC might not have the needed ADC/DAC onboard, but a networkattached Remote Interface Unit (RIU) with ADC/DAC capabilities can be provided at or near the vehicle's sensors and actuators. (See Figure 2 for a networkcentric reference design.) The RIU in this case would digitize the inputs, communicate with the SBC through a standard network interface such as GbE, and generate analog outputs, therefore creating a standardized interface between the processor and the I/Os. The same approach is also applicable to Network Attached Storage (NAS). NAS improves data accessibility via Network File System (NFS) protocol while making it seamless to grow the storage capacity on the network at a later time. As long as the new device conforms to the same GbE and the file sharing protocols, the rest of the system is not impacted.

Traditionally, the inputs from platformspecific sensors are either hardwired directly to the processor or transmitted over MIL-STD-1553 or ARINC-429 buses, and the processor board must be

designed with dedicated signals such as discrete, analog I/O MIL-STD-1553/ ARINC-429 bus interfaces to handle that communication. This introduces an obsolescence risk as the support for

For more information, visit www.zmicro.com/zx or call 858.831.7054.

these special signals is not standardized by the industry. In other words, a custom product has to be made, which comes at steep nonrecurring and recurring prices. To eliminate those issues, taking the RIU approach, network-attached sensors and effectors can use GbE to communicate through network switches, freeing the processor card from requiring any special onboard I/O. This permits the sensor to stay in place while the processor card or electronic system can be replaced or upgraded separately, with the added benefit of reduced wire counts in the main harness assemblies. Combined with

deterministic Ethernet, like ARINC-664/ AFDX for avionics, flight control needs can be met.

### VPX and high-speed serial fabrics

Another advantage of embracing new open architectures on UAVs is their support for distributed computing. In today's systems, it is typical for each of the multiple SBCs to be assigned specific functions. Density limits on SBCs, currently at around 18 GFLOPS for a conductioncooled 3U card, mean that the requirements frequently can't be addressed in a single slot. A distributed or cluster

Figure 3 | A ruggedized electronic enclosure that can support high-speed interfaces and be cooled in different ways in accordance with VITA 48.x.

environment, on the other hand, enables tasks to be shared amongst the SBCs, effectively multiplying CPU power to the 100s of GFLOPS required by video processing and intelligent algorithms. Working in unison with RIUs, the processors can now be physically relocated to practically anywhere within the airframe where CPU power, electronics packaging, power supplies, and cooling capacities can be managed more effectively and where space is available. Figure 3 shows a ruggedized electronic enclosure that supports high-speed interfaces and can be cooled

in different ways in accordance with

VITA 48.x.

This type of processor-to-processor collaboration essentially takes the Symmetric Multi-Processing (SMP) and multicore model beyond the slot level to the chassis level and beyond. This collaboration requires high-speed interconnects, often at multiple Gigabytesper-second speeds, and is now possible via open standards such as VPX (VITA 46) and its support for serial fabrics such as Serial RapidIO and PCIe. The newer OpenVPX (VITA 65) further refines pinout definition for interoperability. External communications outside the chassis can be achieved with GbE and 10 GbE. One way to satisfy the growing hunger for more processing is to standardize on communications protocols that support distributed computing.

### **Bridging with legacy devices**

As UAV platforms migrate to a networkcentric approach, legacy buses such as 1553, RS-232, and CANbus will need to communicate with newer GbE-based interfaces through bridge devices. This approach allows for an incremental upgrade that matches today's existing

budget constraints, because it is unlikely that all older LRUs can be replaced at the same time. There will be a period of time during which new electronic systems and older ones based on the legacy interfaces must coexist.

Curtiss-Wright Controls Electronic Systems' network bridge technology is used in sensor management and payload management computers to integrate legacy, proprietary, and emerging interfaces in addition to performing data fusion by translating the communications protocols from one side to another. For example, when it is time to upgrade a Remote Terminal (RT) from the 1553 network and put it onto the GbE side, the network bridge can transparently emulate the RT's I/O as though it were still on the 1553 side. The other LRUs on the UAV won't even detect that the RT has been transitioned to the GbE side. The same can be achieved for Bus Monitors (BMs) and Bus Controllers (BCs).

### Thinking ahead

The demand for electronic systems with advanced multiprocessor compute technologies on tactical and strategic UAVs creates many challenges. Open interface standards such as VPX (VITA 46), OpenVPX (VITA 65), and VPX-REDI (VITA 48) - along with adoption of standardized high-speed interconnects like GbE and PCIe - enable designers to overcome these challenges. Also critical to the equation is the ability to bridge legacy devices. Hence, now is the time for designers to optimize their electronic systems with a network-centric, open architecture approach to achieve new levels of processing efficiencies and performance.  $\oplus$

David W. Lee is a Project Engineer for Curtiss-Wright Controls Electronic Systems. He has more than 12 years of experience in avionics and

embedded systems. He holds a degree in Computer Science from the University of Buffalo and an MS in Computer Science from Binghamton University. He can be contacted at dlee@curtisswright.com.

> **Curtiss-Wright Controls Electronic Systems** 661-257-4430 www.cwcelectronicsystems.com

### SEALEVEL

Computing/HMI | Serial | I/O

### The right connection creates incredible power.

Connectivity and control. Making your interface as reliable as the tides—and just as strong. Sealevel creates hardware and software solutions for both digital and serial interface requirements. We Listen. Think. And Create.

Experience exceptional computing at low power with the SBC-R9, an application-ready platform for your next product design.

sealevel.com > sales@sealevel.com > 864.843.4343

A broad range of embedded computing form factor options matches diverse airframe size and mission requirements for today's UAVs and UASs.

"We have just won a war with a lot of heroes flying around in planes. The next war may be fought by airplanes with no men in them at all. It certainly will be fought with planes so far superior to those we have now that there will be no basis for comparison. Take everything you've learned about aviation in war, throw it out of the window, and let's go to work on tomorrow's aviation. It will be different from anything the world has ever seen," said Gen Hap Arnold, U.S. Army Air Forces (USAAF), on VJ Day, 1945[1].

Unmanned Aerial Vehicles (UAVs) and Unmanned Aerial Systems (UASs) are proving General Arnold's visionary

thinking, as they emerge as two of today's most adaptable, in-demand military technologies. These programs offer endurance, efficiency, flexible mission management, attack capability, information collection, and connectivity: valuable attributes that enable military command to effectively and safely multiply forces. The vision for these unmanned systems is to harness their intrinsic benefits for automated, modular, globally connected and sustainable multi-mission purposes that maximize force utilization. The U.S. Air Force's UAS Flight Plan has predicted a leaner, more adaptable and efficient air force encompassing a broad family of

unmanned aircraft that reaches well past the earliest strictly surveillance-based predecessors.

As new UAS applications go beyond mere surveillance to encompass small man-portable vehicles (even micro- and nano-sized), medium "fighter sized" vehicles, large "tanker sized" vehicles, and special vehicles with unique capabilities, there is a significant requirement to expand the embedded computing technology that controls them. This increased diversity in UAS applications and functionality supports the U.S. DoD's longterm commitment to sophisticated, technology-supported warfare. Making

this commitment a reality will challenge future UAS designs to combine multimission, ultra-rugged, net-centric, modular, open architecture features capable of carrying any standard payload within their given performance envelope.

Embedded technology advancements and a broad range of COTS form factors have become key enablers of new modular UAS/UAV platforms. The good news is that UAS designers have a wide arsenal of open architecture COTS form factors that will satisfy evolving SWaP, performance, space constraint, extended temperature, and sophisticated signalprocessing requirements. Determining the optimal form factor for a particular UAS/UAV design requires a deep level of expertise and an understanding of the advantages and design trade-offs provided by the range of embedded computing alternatives.

### **Open architecture COTS form** factor options

In this maze of embedded design challenges, sticking to a single computing form factor for all UAV/UAS designs is not really a relevant approach. Instead, designers must leverage and evaluate a varied slate of standards-based options. The optimal embedded computing choice meets the desired program and UAS/UAV platform goals by matching the airframe requirements and creating interoperable, COTS-based systems that integrate with the Joint Forces' worldwide information network. This includes adding capabilities such as payload, networking, and effective data processing, analysis, and dissemination. The demand is rising for netcentric implementations that enable soldiers, military systems, and equipment to share real-time information with higher bandwidth and increased computing performance. So is the need to upgrade embedded computers in existing deployed units.

From the ultra-rugged VPX to small Computers-on-Module (COMs), highbandwidth MicroTCA, and proven CompactPCI, designers now have a richer and broader variety of proven COTS embedded computing form factor options. Designers can also leverage continued advancements to standards-based technologies to achieve their varied and evolving UAS/UAV platform objectives. Since the landscape of available open architecture form factors covers a wide set of technologies, it is wise to evaluate each on its strengths for a particular application.

### VPX for high-speed signal processing

UAS payloads (short-, medium-, or longrange airframes) may include communications, signals intelligence, high-resolution Synthetic Aperture Radar (SAR), imaging systems, or even weaponry. Improved situational awareness is the primary goal, downloading compressed, live video or other information to a portable device on the ground. As a result, image compression and bandwidth demand much of the system designer's attention. Largely based on its ability to provide high-frequency processing as well as a reliable fabric solution, rugged VPX is emerging as an ideal platform for these data-intensive UAV applications (Figure 1).

Figure 1 | Rugged VPX technologies are emerging as an ideal platform for data-intensive UAV applications, Pictured: The Kontron VPX Blade VX6060, with two independently implemented Intel Core i7 processing nodes linked to an Ethernet and PCle infrastructure.

VPX enables higher performance processing per slot but also higher-speed interconnects between processing and I/O elements using PCIe, 10 GbE, or Serial RapidIO. These interconnects provide 10 Gbps between elements or several hundred GBps in aggregate, depending on the system implementation. Handling the increased signal rates that characterize high-bandwidth, highperformance UAS applications, VPX systems can achieve greater than 5 GBps using a number of different serial fabric technologies. Full-mesh architectures, not available in VMEbus systems, enable

system aggregate bandwidth greater than 100 GBps.

The VPX platform builds on VME's processing capabilities, combining robustness and excellent EMC - fundamental strengths of the VMEbus architecture with new high-bandwidth serial interconnects for high-speed differential signaling over the backplane. VPX leverages more I/O per slot – for example, taking data in a fast 10 GbE data rate and dispatching it to several processors that manage the workload in parallel - and maximizes higher computing density from available processors and chipsets. This is in contrast to VMEbus platforms primarily using parallel bus technology that provided successive bandwidth improvement over the years, starting with 40 MBps and evolving to today's 320 MBps.

As an example of VPX's suitability for applications that require video-streaming capabilities, VPX can be integrated with codecs including ITU-T H.263, H.264 (MPEG-4 part 10), and JPEG2000 to provide very efficient image compression. The H.264 codec is particularly optimized for streaming and offers extremely efficient compression by providing the capability to trade off image quality or compression as the available bandwidth changes. This flexibility makes using VPX with this codec a viable option for supporting UAS video payload applications that can be required to operate over a number of data link options and operational scenarios.

### MicroTCA meets rugged, high-bandwidth needs

Range and altitude may be deciding factors in choosing an embedded computing form factor. UAS platforms that need to perform in longer-range missions will typically need to operate at higher altitudes as well (Figure 2). Then there are range and altitude requirements for extended loitering capabilities, too, which all translates into the need for a rugged and reliable form factor in terms of power, weight, and thermal management.

A case in point is that a larger airframe may have an avionics bay containing forced-air cooling, where many smaller airframes do not offer that capacity. Rugged air-cooled MicroTCA (MTCA.1), hardened MicroTCA (MTCA.2), and conduction-cooled MicroTCA (MTCA.3) leverage the ANSI/VITA 47 specification to define these types of environmental requirements.

MTCA.1 extends MicroTCA into more rugged military environments as defined by ANSI/VITA 47's EAC6 environmental class and V2 vibration class. The new MTCA.3 spec is now underway with PICMG and is expected to define a conduction-cooled interface that meets the most extreme thermal, shock, and vibration profiles defined in ANSI/ VITA 47 (that is, performing in conduction-cooled systems with no airflow within sealed environments, common to space-constrained UAS applications).

Figure 2 | Vertical Takeoff and Landing Tactical UAVs (VTUAVs) can take off and land in rugged or unimproved terrain in close proximity to troop and tactical operations centers. Acting as a communications node within the Joint Tactical Radio System (JTRS), they extend both network effectiveness and flexibility.

These options highlight MicroTCA as a cost-effective alternative to the ultrarugged VPX; MicroTCA is characterized by high processing capacity, extremely high communication bandwidth, and high availability designed into a small form factor. A 3U or 4U system, tapping up to 12 compute blades on a single backplane all potentially using a multicore processor, could be integrated with as many as 24 cores in a very small footprint. Designers using MicroTCA can also leverage as many as 21 high-speed serial connections on the backplane, each delivering bandwidth of 2.5 Gbps. Depending on the airframe or its ground control system, as well as how each system is implemented, an extensive range of MicroTCA-based communications bandwidth capacities is available, ranging from 40 Gbps to >1 Tbps. When contrasted to VPX's 80 GBps aggregate bandwidth, designers need to additionally understand that VPX also defines a larger quantity of user I/O options not defined in the MicroTCA spec.

### CompactPCI: Proven rugged, long-term reliability

CompactPCI also provides notable bandwidth, performance, and cooling options. Its status as a mainstay UAS platform is based on advantages such as its inherent ruggedness, rear I/O, support for the full range of high-speed interfaces, and an extensive range of PCI-compatible software. With improvements in space and energy savings enabled by advancements such as Intel's 32 nm, Atom-based low-power processors and multicore architectures, many designers consider CompactPCI ideal for a self-contained network implementation managing multiple blades communicating over GbE in a single backplane. Even though CompactPCI is largely limited to 1 GB speeds and parallel PCI - dramatically reduced bandwidth as compared to a VPX backplane - it uses the same 3U/6U mechanics and so can readily accommodate the same rugged environments.